このところ連日ATU-100の話になっていますが、細かいところで悩みどころが多く逆にやり甲斐があります。今回は、ATUからシャックに引き込む信号線について考えました。

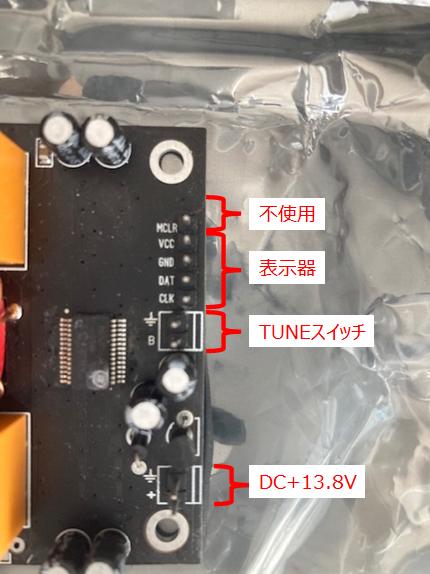

まずは基板の表面です。

下から主電源(DC+13.8V)、TUNEスイッチ用信号線、I/O信号線(CLK, DAT, GND, VCC, MCLR)です。このI/O信号線はプログラミングや表示出力に使うようですが、このうちMCLRはプログラミング制御や本体リセット用としてリモートで使うことは想定されませんので、そのままオープンにしておきます。

なお、回路図を見るとMCLRは10KΩでプルアップされていますが、かつてページャの設計をしていたとき消費電流の関係でCMOS入力のプルアップは基本的に1MΩだったので少し違和感があります。でもこの端子は定常的に使うものではなく、また外部のノイズによって頻繁にリセットされてもまずいので、この程度の抵抗値が適当なのかと思いました。

ちなみにプロセッサは「PIC16F1938-I/SS」という28ピンのSSOPで、データシートはこちらから参照できます。P.77 §6.4.1のMCLRの説明に「The MCLR pin is connected to VDD through an internal weak pull-up.」との記述があり、MCLRは内部の「弱い(=抵抗値の大きい)」プルアップでVDDにつながっているとのことです。ATUのように外からノイズを受け易い環境ではそれだけでは不足なのかも知れません。

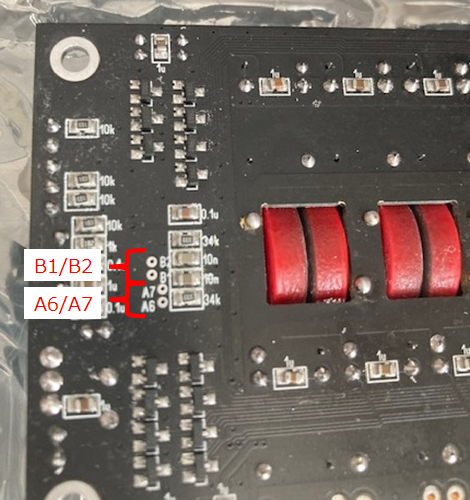

次に基板の裏面です。

ATU-100のマニュアルによると、RB1はAUTOスイッチ、RB2はBYPASSスイッチとのことです。それぞれ写真のB1とB2です。またRA6とRA7(写真のA6とA7)はリグのTX ONコントロール用で、当面は使わないでしょうが一応シャックまで引いておきたいと思います。RA6とRA7は極性が逆とのことでリグによってどちらか使い分ければ良いと理解しました。なお、シャック側のスイッチは、電源以外はチャタリングやノイズ除けのコンデンサが必要ですね。

今後、また細かい材料などを集める必要があり完成はいつになるのか・・・納期を気にすることも無いので、自分のペースでのんびり進めていきます。